The modern data center is currently navigating a period of unprecedented architectural transformation, driven primarily by the insatiable demands of artificial intelligence, machine learning, and high-performance computing (HPC). As processing power continues to scale according to Moore’s Law, the industry has encountered a formidable obstacle often referred to as the "memory wall." This bottleneck is characterized by the growing disparity between the speed of central processing units (CPUs) and the latency and bandwidth of the memory systems that feed them. Central to this challenge is the physical movement of data; in contemporary high-performance environments, the energy and time required to move data between storage, memory, and the processor have become the primary constraints on system efficiency.

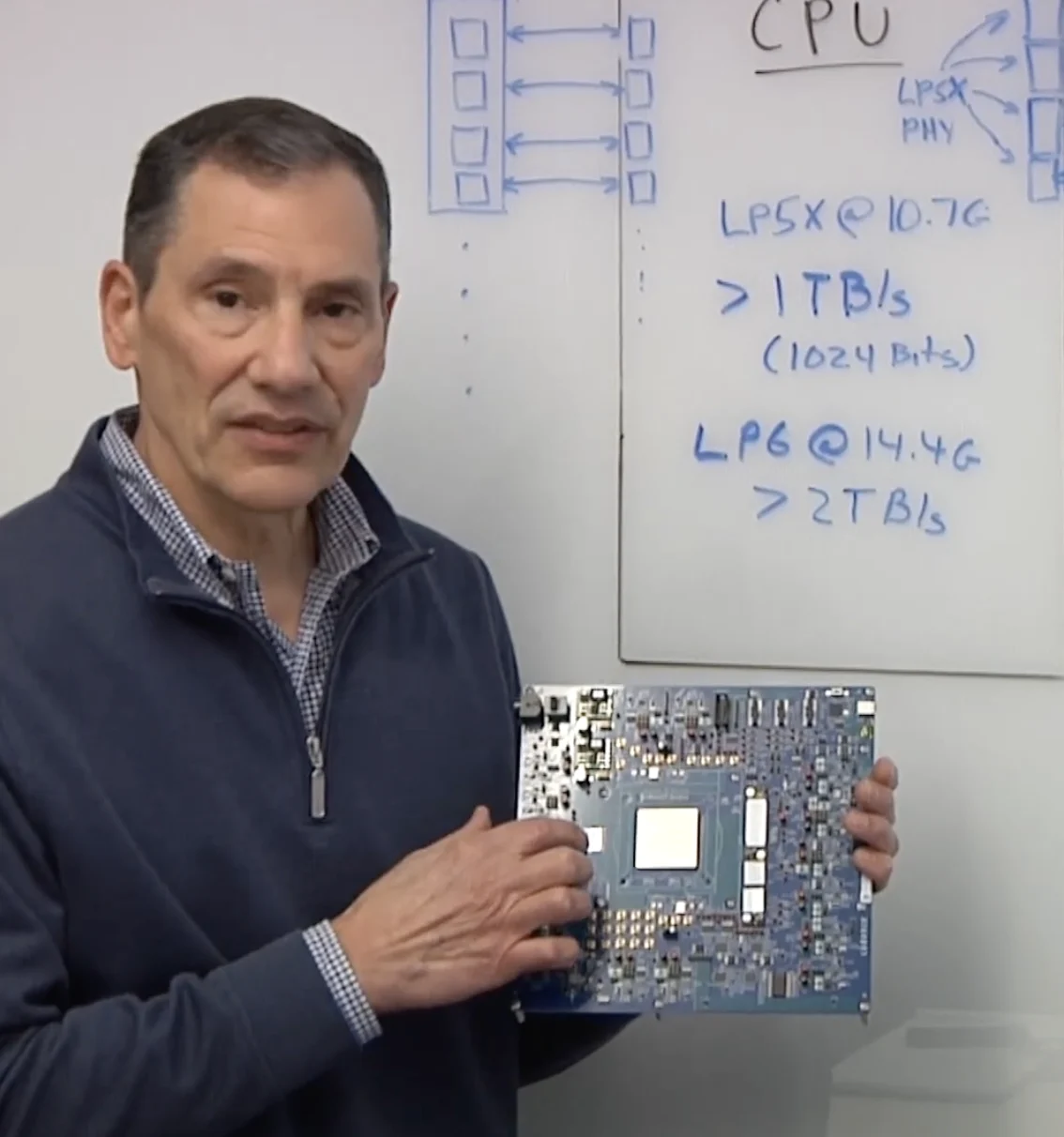

Small Outline Compression Attached Memory Modules (SOCAMMs) have emerged as a critical innovation designed to address these constraints. By bridging the gap between the high density of traditional server memory and the low-power requirements of mobile-grade components, SOCAMMs represent a significant shift in how memory is integrated into high-performance systems. Frank Ferro, group director for product management at Cadence, recently highlighted that the transition toward modular, low-power standards is not merely a matter of convenience, but a necessity for the next generation of data center infrastructure.

The Technical Evolution from SODIMM to SOCAMM

For decades, the Small Outline Dual In-line Memory Module (SODIMM) was the industry standard for compact memory applications. However, as data rates transitioned from DDR4 to DDR5 and now look toward DDR6, the physical limitations of the SODIMM architecture have become apparent. SODIMMs rely on a pin-and-socket mechanism that introduces significant "stubs"—short lengths of unused electrical traces—which cause signal reflections and electromagnetic interference at high frequencies. When memory speeds exceed 6400 MT/s (MegaTransfers per second), the signal integrity of a traditional SODIMM degrades to the point where reliable data transmission becomes nearly impossible without complex and power-hungry equalization techniques.

SOCAMM, and the broader JEDEC-standardized CAMM2 (Compression Attached Memory Module) framework, solves this by replacing the vertical socket with a land grid array (LGA) style compression connector. This design allows the memory module to sit flat against the motherboard, significantly shortening the electrical path between the memory controller and the DRAM chips. By reducing the distance and eliminating the parasitic capacitance associated with traditional slots, SOCAMM enables much higher clock speeds while maintaining the modularity that data center operators require for repairs and upgrades.

Chronology of Modular Memory Standardization

The path to SOCAMM began with a proprietary push for better form factors in the laptop market. In 2022, Dell introduced the initial CAMM design to overcome the thickness and speed limitations of SODIMMs in high-end workstations. Recognizing the potential for industry-wide adoption, the design was submitted to JEDEC, the global leader in developing open standards for the microelectronics industry.

In late 2023, JEDEC formally published the JESD318 standard for CAMM2. This standardization was a pivotal moment, as it defined two distinct branches: one for DDR5 and another for LPDDR5/5X. The latter is particularly significant for the HPC and data center markets. Traditionally, LPDDR (Low Power DDR) memory had to be soldered directly onto the motherboard to maintain signal integrity, which made repairs impossible and limited scalability. The introduction of SOCAMM/CAMM2 allows LPDDR5X to be used in a modular format for the first time, combining mobile-class power efficiency with enterprise-class flexibility.

By mid-2024, leading IP and silicon providers like Cadence began integrating SOCAMM support into their memory controller and PHY (Physical Layer) offerings. This allowed chip designers to start building processors that could natively communicate with these new modules, setting the stage for a wide-scale rollout in the 2025-2026 server refresh cycles.

Solving the Thermal and Power Crisis in Data Centers

One of the most compelling arguments for the adoption of SOCAMM in high-performance environments is its impact on thermal management. In a traditional data center rack, cooling accounts for approximately 30% to 40% of total energy consumption. As AI accelerators and high-core-count CPUs push thermal design power (TDP) toward 500W and beyond, the heat generated by memory becomes a compounding problem.

Standard DDR5 modules generate significant heat due to their higher operating voltages and the power-hungry logic required to maintain signal integrity over long traces. In contrast, SOCAMMs utilizing LPDDR5X operate at lower voltages (1.05V vs. 1.1V or higher for standard DDR5) and benefit from the inherently lower power profile of mobile DRAM.

Frank Ferro notes that the move to SOCAMM can potentially allow system designers to avoid active cooling—such as dedicated fans or complex liquid cooling loops—for the memory subsystem. Because the module is compressed directly against the PCB and has a thinner profile, it facilitates better airflow across the chassis. Furthermore, the reduction in power consumption directly translates to a lower heat signature. In massive-scale deployments, saving even 2 to 3 watts per module can result in megawatts of power savings across a data center facility, significantly improving Power Usage Effectiveness (PUE) scores.

Performance Metrics and Comparative Analysis

When comparing SOCAMM to existing memory standards, the performance gains are measurable and significant. Current LPDDR5X SOCAMMs are capable of reaching speeds of 8533 MT/s, with roadmaps extending toward 9600 MT/s and beyond.

| Feature | SODIMM (DDR5) | SOCAMM (LPDDR5X) |

|---|---|---|

| Max Data Rate | ~6400 MT/s | 8533+ MT/s |

| Voltage | 1.1V | 1.05V |

| Connection Type | Pin-and-Socket | Compression (LGA) |

| Modularity | High | High |

| Signal Integrity | Limited by stubs | Optimized/Short path |

| Height Profile | ~4.0 mm – 9.0 mm | ~1.5 mm |

The data indicates that SOCAMM provides a "best of both worlds" scenario. It offers the speed and power efficiency of soldered-down LPDDR memory while retaining the serviceability of a plug-in module. For HPC providers, this means they can density-optimize their blade servers, fitting more memory and processing power into a 1U or 2U chassis without exceeding thermal limits.

Industry Reactions and Market Adoption

The shift toward SOCAMM has seen a positive reception from various sectors of the technology stack. Hyperscale cloud providers, including Amazon Web Services (AWS) and Google Cloud, have expressed a vested interest in any technology that reduces the Total Cost of Ownership (TCO) through energy savings. While these companies often use custom-designed hardware, the move toward a standardized modular low-power format allows for a more robust supply chain.

Memory manufacturers such as Micron, Samsung, and SK Hynix have already begun showcasing CAMM2 and SOCAMM-compliant modules. Micron, in particular, has been vocal about the role of these modules in the "AI PC" and "Edge AI" sectors, where high-speed memory is required to run Large Language Models (LLMs) locally without draining battery life or overheating compact enclosures.

Cadence’s Frank Ferro emphasizes that the industry is at a crossroads where the physical architecture of the computer must change to keep up with software demands. He suggests that while DDR5 will remain the workhorse for high-capacity applications, SOCAMM will become the standard for "performance-per-watt" sensitive applications. This includes edge servers, where environmental controls are less stringent than in centralized data centers, and active cooling is often not an option.

Broader Implications for the Future of Computing

The implications of SOCAMM extend beyond simple hardware specifications; they represent a fundamental change in the philosophy of system design. By moving toward compression-attached interfaces, the industry is signaling that the era of the "one-size-fits-all" memory slot is ending.

In the long term, the SOCAMM standard paves the way for more exotic memory types to enter the modular market. As we look toward the development of LPDDR6, the lessons learned from SOCAMM’s compression interface will be vital. The industry is already discussing the possibility of "optical CAMMs" or modules that integrate advanced photonic interconnects directly onto the memory board to further reduce latency.

Moreover, SOCAMM contributes to the growing movement for "Right to Repair" and sustainability in the enterprise space. By moving away from soldered-down components, manufacturers can reduce e-waste. If a single memory chip fails on a soldered motherboard, the entire board often must be replaced. With SOCAMM, the specific module can be swapped out in seconds, extending the lifecycle of the server hardware and reducing the carbon footprint of the data center.

Conclusion: A New Standard for the AI Era

The transition to SOCAMM is a pragmatic response to the dual pressures of increasing data velocity and the urgent need for energy efficiency. As AI continues to permeate every facet of enterprise computing, the infrastructure supporting it must be both agile and efficient. By eliminating the electrical bottlenecks of traditional slots and embracing the low-power advantages of LPDDR technology, SOCAMM provides a clear path forward for high-performance compute.

While challenges remain—including the initial cost of transitioning manufacturing lines and the need for widespread motherboard redesigns—the momentum behind SOCAMM is undeniable. With the backing of major standards bodies like JEDEC and industry leaders like Cadence, the Small Outline Compression Attached Memory Module is set to become a cornerstone of the next generation of efficient, high-performance digital infrastructure. The data center of tomorrow will be defined by its ability to move data intelligently, and SOCAMM is the mechanism that will make that movement possible.