The global semiconductor industry is currently navigating a pivotal transition that marks the end of an era defined solely by traditional transistor scaling. For decades, Moore’s Law—the observation that the number of transistors on a microchip doubles approximately every two years—served as the primary roadmap for performance gains. However, as physical limits and economic costs of sub-3nm nodes increase, the industry has shifted its focus toward advanced packaging. This movement, often referred to as "More than Moore," utilizes 2.5D, 3D-ICs, chiplets, and heterogeneous integration to achieve the performance and bandwidth required by modern computing. While these architectures provide a pathway to unprecedented computational power, they have simultaneously introduced a radical increase in power delivery complexity. In this new landscape, power integrity (PI) has emerged as the most critical constraint in system design, necessitating a fundamental shift from localized die-level analysis to a comprehensive system-level discipline.

The Architectural Shift: From Planar to Three-Dimensional Power Networks

The transition from traditional 2D System-on-Chips (SoCs) to 3D-ICs represents a departure from horizontal engineering. In a standard 2D environment, power delivery networks (PDN) were largely planar. Engineers managed horizontal current flow and noise behavior that was relatively localized and predictable. The introduction of 3D-ICs, however, brings vertically stacked power paths that span multiple layers, including dies, silicon interposers, micro-bumps, through-silicon vias (TSVs), and package planes.

This verticality creates a highly complex web of connectivity. In a 3D stack, a disturbance in one region—such as a high-performance accelerator core drawing a sudden burst of current—can manifest as a voltage drop or electromagnetic interference in a completely different die within the stack. Because these components are physically and electrically coupled, power integrity can no longer be treated as a per-die concern. It has become a three-dimensional, system-scale problem where the performance of the top-most logic layer is inextricably linked to the electrical stability of the layers beneath it.

A Chronology of Advanced Packaging Evolution

To understand the current state of power integrity, one must look at the chronological progression of packaging technology over the last decade.

In the early 2010s, the industry began widely adopting 2.5D integration, most notably seen in the development of High Bandwidth Memory (HBM). This involved placing logic and memory side-by-side on a silicon interposer, using TSVs to connect to the substrate. This era focused on reducing the distance between memory and processors to overcome the "memory wall."

By the late 2010s, the "Chiplet" revolution took hold. Companies like AMD and Intel began decomposing large monolithic dies into smaller functional blocks (chiplets) manufactured at different process nodes. This approach improved yields and reduced costs but increased the demand for dense interconnects.

Entering the 2020s, the industry moved toward true 3D-IC stacking (logic-on-logic and logic-on-memory). This stage has been accelerated by the explosion of generative AI and Large Language Models (LLMs), which require massive computational density. Today, the focus has shifted entirely to managing the "Power Wall"—the limit at which heat dissipation and power delivery constraints prevent further performance increases.

The Impact of Interconnect Density on Power Stability

The drive for higher bandwidth in AI and High-Performance Computing (HPC) has led to an exponential increase in interconnect density. Modern 3D systems may incorporate tens of thousands of micro-bumps and dense TSV arrays to facilitate the necessary VDD and VSS connections. While this density allows for massive data throughput, it exposes new and dangerous failure modes for power integrity.

One of the primary concerns is the increased susceptibility to electromigration and IR-drop. As voltage margins continue to shrink—often dropping below 0.8V for advanced logic—even a minor millivolt fluctuation can lead to logic errors or timing violations. Furthermore, the sheer volume of connections makes the PDN highly sensitive to manufacturing variations. In AI/ML systems, where compute patterns are inherently "bursty," the fast current transients can cause significant inductive noise (L di/dt). Without high-accuracy modeling of these dense interconnects, engineers risk over-designing the system, which wastes space and power, or under-designing it, which leads to catastrophic field failures.

The Electro-Thermal Challenge of TSVs and Interposers

In the realm of 2.5D and 3D-ICs, through-silicon vias and interposers are no longer just passive conduits; they are the central nervous system of both power delivery and thermal transport. As TSV counts climb into the tens of thousands, they create a complex multi-physics environment.

Power integrity in 3D-ICs is inherently electro-thermal. Electrical resistance in the TSVs and interposers generates heat (Joule heating), and this temperature rise, in turn, increases the electrical resistance of the metal layers. This creates a feedback loop that can degrade performance if not managed. Furthermore, the different coefficients of thermal expansion (CTE) between the silicon dies, the interposer, and the organic substrate can lead to mechanical stress. This stress can shift the electrical characteristics of the transistors nearby, adding another layer of unpredictability to the PI analysis.

To combat these issues, the industry is exploring advanced thermal strategies such as liquid cooling, direct-to-package cold plates, and even micro-fluidic interposers. While these technologies increase the thermal headroom for AI chips, they also introduce new variables into the power integrity equation, such as the electromagnetic impact of cooling structures and the need for even more precise localized power monitoring.

The Dominance of the Package in High-Frequency Power Delivery

A significant shift in modern semiconductor design is the realization that the package has become a dominant element in the power delivery network. As more power delivery components move off-die to accommodate the limited real estate of 3D stacks, the package must handle a greater share of the mid-to-high frequency decoupling.

For AI workloads, which operate with high-speed switching and rapid state changes, the package-level inductance and capacitance are critical. High-frequency noise can be amplified across multiple dies simultaneously if the package PDN is not optimized. This requires engineers to look beyond DC or low-frequency approximations. Robust signoff now demands frequency-dependent modeling that accounts for the interaction between the die, the interposer, and the substrate across a wide spectrum of operating conditions.

Industry Responses: Moving Toward Unified Workflows

The complexity of 3D-IC power integrity has exposed a significant flaw in traditional design methodologies: fragmentation. Historically, PI analysis has been siloed, with separate teams and tools handling the die, the interposer, and the package. This "black-box" approach often leads to missed interactions at the interfaces, resulting in late-stage design changes that are both costly and time-consuming.

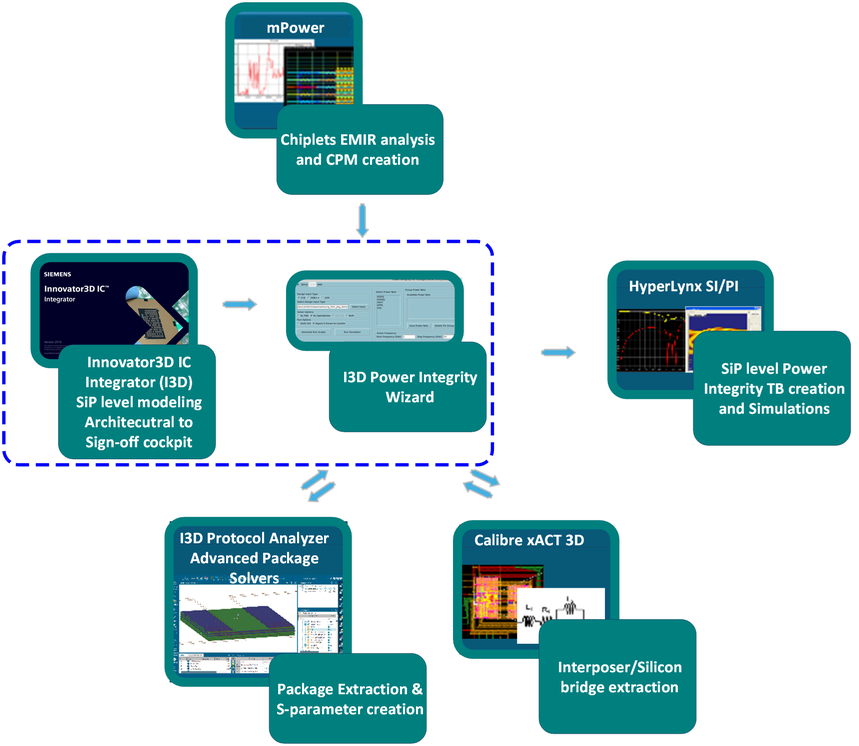

In response, leaders in the Electronic Design Automation (EDA) space, such as Siemens Digital Industries Software, are championing unified, system-centric workflows. By integrating tools like the Innovator3D IC Integrator with established platforms like Calibre, mPower, and Xpedition, engineers can perform concurrent analysis of the entire stack.

These integrated flows allow for:

- System-level extraction: Capturing the parasitic elements of the entire 3D assembly.

- Multi-physics simulation: Simultaneously analyzing electrical, thermal, and mechanical stresses.

- Early-stage exploration: Allowing designers to evaluate different stacking configurations before finalizing the physical layout.

- High-capacity signoff: Handling the massive datasets associated with tens of thousands of TSVs and millions of bumps.

Broader Implications for the Semiconductor Supply Chain

The shift toward system-level power integrity has profound implications for the global semiconductor supply chain and the competitive landscape of the AI era. First, it is redefining the relationship between fabless chip designers and Outsourced Semiconductor Assembly and Test (OSAT) providers. Packaging is no longer a commodity service performed at the end of the manufacturing process; it is a core part of the architectural design that must be co-optimized with the silicon.

Second, the increased difficulty of achieving power integrity signoff is creating a higher barrier to entry for high-end AI hardware. Only companies with access to sophisticated EDA tools and deep expertise in multi-physics simulation can successfully bring 3D-ICs to market. This is driving a wave of consolidation and strategic partnerships across the industry.

Finally, the focus on power integrity is a direct response to the global demand for energy-efficient computing. As data centers consume an ever-increasing share of the world’s electricity, the ability to deliver power efficiently to AI processors is not just a technical requirement—it is an environmental and economic imperative. Reducing voltage drops and optimizing PDNs directly translates to lower power consumption and reduced operational costs for the massive server farms that power the modern digital economy.

Conclusion: The Path Forward for Semiconductor Leaders

As the semiconductor industry enters the age of AI-driven 3D-ICs, the traditional boundaries of chip design are dissolving. Success in this new era requires semiconductor leaders to embrace three fundamental shifts:

- From Component to System: Recognizing that power integrity is a holistic property of the entire 3D stack, not an isolated die-level metric.

- From Electrical to Multi-Physics: Integrating thermal and mechanical considerations into the electrical design process from day one.

- From Fragmented to Unified: Breaking down the silos between design teams and adopting integrated EDA workflows that provide a "single source of truth" for the entire system.

By adopting a system-level approach to power integrity, semiconductor teams can unlock the full performance potential of advanced packaging. This shift not only de-risks the design of complex 2.5D and 3D-ICs but also accelerates the time-to-market for the next generation of AI breakthroughs. The "Power Wall" is a formidable challenge, but with the right tools and a system-centric mindset, it is a hurdle that the industry is well-equipped to overcome.